12 Cisc Vs Risc Tips For Better Coding

The debate between CISC (Complex Instruction Set Computing) and RISC (Reduced Instruction Set Computing) has been a longstanding one in the world of computer architecture. Each has its own strengths and weaknesses, and understanding these differences is crucial for developers looking to optimize their code for performance, power efficiency, and complexity. In this comprehensive guide, we’ll delve into the fundamentals of both CISC and RISC, explore their historical evolution, and provide actionable tips for coding on these architectures.

Introduction to CISC and RISC

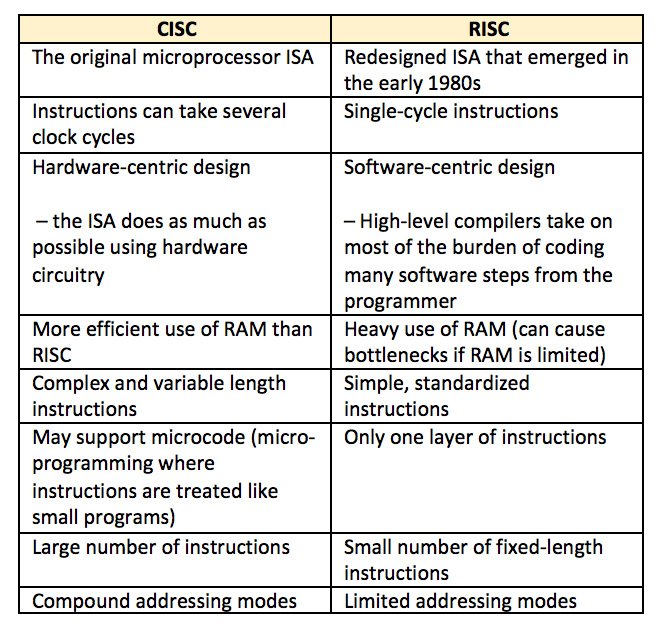

CISC processors are designed to execute complex instructions that can perform multiple operations in a single clock cycle. This approach aims to reduce the number of instructions that need to be fetched and decoded, potentially leading to faster execution times for certain types of code. On the other hand, RISC processors use a simpler instruction set with an emphasis on executing instructions quickly and efficiently. The idea behind RISC is that simpler instructions can be combined to perform complex tasks, potentially leading to better performance and lower power consumption.

Historical Evolution: From CISC to RISC

The evolution from CISC to RISC architectures was largely driven by the challenges faced by CISC in terms of complexity, power consumption, and scalability. As computing demands increased, the need for more efficient and scalable architectures became apparent. RISC architectures, with their simpler and more consistent instruction sets, provided a solution that not only improved performance but also reduced power consumption and heat generation.

Understanding the Key Differences

- Instruction Set Complexity: CISC has a more complex instruction set that can perform more operations per instruction. RISC, however, has a simpler set that emphasizes executing instructions quickly.

- Pipelining: RISC architectures are more amenable to pipelining, a technique that allows for the overlapping of instruction execution stages, improving throughput.

- Code Density: CISC instructions are often more code-dense, requiring fewer instructions to perform a task. However, RISC’s simplicity can lead to more efficient compilation and execution in many cases.

Tips for Better Coding on CISC and RISC

Understand Your Target Architecture: Before you start coding, it’s crucial to understand whether your code will be running on a CISC or RISC processor. This knowledge can help you make informed decisions about optimization.

Optimize for RISC with Loop Unrolling: Since RISC processors execute instructions quickly but may require more instructions for complex tasks, techniques like loop unrolling can help reduce overhead and improve performance.

Use Pipelining Effectively: For RISC architectures, ensuring that your code is pipelined efficiently can significantly improve performance. This might involve reordering instructions to minimize dependencies.

Leverage SIMD Instructions: Both CISC and RISC architectures often support SIMD (Single Instruction, Multiple Data) instructions. Using these can greatly improve performance in tasks that involve parallel operations.

Minimize Branch Prediction Errors: For both architectures, reducing branch prediction errors can improve performance. Techniques like aligning code to cache lines and using branch prediction hints can be beneficial.

Profile Your Code: Regardless of the architecture, profiling your code to understand where bottlenecks occur is essential. This can help you target your optimization efforts effectively.

Consider Power Consumption: Especially in mobile and embedded systems, power efficiency is crucial. RISC architectures often have an advantage here due to their simpler design and lower switching activity.

Use Compiler Optimizations: Modern compilers are very good at optimizing code for the target architecture. Make sure to use the appropriate optimization flags for your compiler and target platform.

Learn Assembly for Deep Optimization: For critical code paths, understanding assembly language for your target architecture can provide insights into how your code is executed and allow for manual optimizations.

Stay Updated with Architectural Advances: The landscape of computer architecture is continuously evolving, with new features and technologies being introduced. Staying informed can help you leverage these advancements in your coding practices.

Use High-Level Abstractions: While understanding low-level details is important, using high-level abstractions and libraries can often lead to more efficient code, as these are typically optimized for the target platform.

Test Across Different Architectures: If possible, test your code on different architectures to understand how it performs. This can reveal optimization opportunities that are specific to one architecture or the other.

Conclusion

In conclusion, while the debate between CISC and RISC continues, the most important factor for developers is understanding how to optimize their code for the target architecture. By grasping the fundamental differences between CISC and RISC, leveraging optimization techniques, and staying updated with the latest developments in computer architecture, developers can write more efficient, scalable, and powerful code.

FAQ Section

What is the primary advantage of RISC over CISC architectures?

+The primary advantage of RISC architectures is their ability to execute instructions quickly and efficiently, leading to better performance and lower power consumption in many applications.

How does pipelining improve performance in RISC architectures?

+Pipelining allows for the overlapping of instruction execution stages, improving throughput by ensuring that the processor is always executing an instruction, rather than waiting for the previous one to complete.

What role does compiler optimization play in coding for CISC and RISC architectures?

+Compiler optimization plays a crucial role as it can significantly improve the performance of code on both CISC and RISC architectures by generating efficient machine code that leverages the strengths of the target platform.

How can understanding assembly language help in optimizing code for specific architectures?

+Understanding assembly language provides insights into how high-level code is translated into machine-specific instructions, allowing developers to identify bottlenecks and manually optimize critical code paths for better performance.

What is the significance of testing code across different architectures?

+Testing code across different architectures helps in identifying optimization opportunities that are specific to one architecture, ensuring that the code is efficient, scalable, and performs well across various platforms.

How does the choice between CISC and RISC affect power consumption in devices?

+RISC architectures generally tend to consume less power due to their simpler design, which results in lower switching activity and heat generation. This makes RISC a preferable choice for battery-powered and energy-efficient devices.